# Foundation Series 4 User Guide

**Chapter 1- Introduction**

Chapter 2 - Project Toolset

Chapter 3 - Design Methodologies - Schematic Flow

Chapter 4 - Schematic Design Entry

Chapter 5 - Design Methodologies - HDL Flow

Chapter 6 - HDL Design Entry and Synthesis

Chapter 7 - State Machine Designs

Chapter 8 - LogiBLOX

Chapter 9 - CORE Generator System

Chapter 10 - Functional Simulation

Chapter 11 - Design Implementation

Chapter 12 - Verification and Programming

Appendix A - Instantiated Components

Glossary

The Xilinx logo shown above is a registered trademark of Xilinx, Inc.

FPGA Architect, FPGA Foundry, NeoCAD, NeoCAD EPIC, NeoCAD PRISM, NeoROUTE, Timing Wizard, TRACE, XACT, XILINX, XC2064, XC3090, XC4005, XC5210, and XC-DS501 are registered trademarks of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

All XC-prefix product designations, Alliance Series, AllianceCORE, BITA, CLC, Configurable Logic Cell, Dual Block, EZTag, FastCLK, FastCONNECT, FastFLASH, FastMap, Foundation, HardWire, LCA, LogiBLOX, Logic Cell, LogiCORE, LogicProfessor, MicroVia, Plus Logic, PLUSASM, Plustran, P+, PowerGuide, PowerMaze, SelectI/O, Select-RAM+, Smartguide, SmartSearch, Smartspec, Spartan, TrueMap, UIM, VectorMaze, VersaBlock, VersaRing, Virtex, WebLINX, XABEL, XACTstep, XACTstep Advanced, XACTstep Foundry, XACT-Floorplanner, XACT-Performance, XAM, XAPP, X-BLOX, X-BLOX plus, XChecker, XDM, XDS, XEPLD, Xilinx Foundation Series, XPP, XSI, and ZERO+ are trademarks of Xilinx, Inc. The Programmable Logic Company and The Programmable Gate Array Company are service marks of Xilinx, Inc.

All other trademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx, Inc. devices and products are protected under one or more of the following U.S. Patents: 4,642,487; 4,695,740; 4,706,216; 4,713,557; 4,746,822; 4,750,155; 4,758,985; 4,820,937; 4,821,233; 4,835,418; 4,855,619; 4,855,669; 4,902,910; 4,940,909; 4,967,107; 5,012,135; 5,023,606; 5,028,821; 5,047,710; 5,068,603; 5,140,193; 5,148,390; 5,155,432; 5,166,858; 5,224,056; 5,243,238; 5,245,277; 5,267,187; 5,291,079; 5,295,090; 5,302,866; 5,319,252; 5,319,254; 5,321,704; 5,329,174; 5,329,181; 5,331,220; 5,331,226; 5,332,929; 5,337,255; 5,343,406; 5,349,248; 5,349,249; 5,349,250; 5,349,691; 5,357,153; 5,360,747; 5,361,229; 5,362,999; 5,365,125; 5,367,207; 5,386,154; 5,394,104; 5,399,924; 5,399,925; 5,410,189; 5,410,194; 5,414,377; 5,422,833; 5,426,378; 5,426,379; 5,430,687; 5,432,719; 5,448,181; 5,448,493; 5,450,021; 5,450,022; 5,453,706; 5,455,525; 5,466,117; 5,469,003; 5,475,253; 5,477,414; 5,481,206; 5,483,478; 5,486,707; 5,486,776; 5,488,316; 5,489,858; 5,489,866; 5,491,353; 5,495,196; 5,498,979; 5,498,989; 5,499,192; 5,500,608; 5,500,609; 5,502,000; 5,502,440; 5,504,439; 5,506,518; 5,506,523; 5,506,878; 5,513,124; 5,517,135; 5,521,835; 5,521,837; 5,523,963; 5,523,971; 5,524,097; 5,526,322; 5,528,169; 5,528,176; 5,530,378; 5,530,384; 5,546,018; 5,550,839; 5,550,843; 5,552,722; 5,553,001; 5,559,751; 5,561,367; 5,561,629; 5,561,631; 5,563,527; 5,563,528; 5,563,529; 5,563,827; 5,565,792; 5,566,123; 5,570,051; 5,574,634; 5,574,655; 5,578,946; 5,581,198; 5,581,199; 5,581,738; 5,583,450; 5,583,452; 5,592,105; 5,594,367; 5,598,424; 5,600,263; 5,600,264; 5,600,271; 5,600,597; 5,608,342; 5,610,536; 5,610,790; 5,610,829; 5,612,633; 5,617,021; 5,617,041; 5,617,327; 5,617,573; 5,623,387; 5,627,480; 5,629,637; 5,629,886; 5,631,577; 5,631,583; 5,635,851; 5,636,368; 5,640,106; 5,642,058; 5,646,545; 5,646,547; 5,646,564; 5,646,903; 5,648,732; 5,648,913; 5,650,672; 5,650,946; 5,652,904; 5,654,631; 5,656,950; 5,657,290; 5,659,484; 5,661,660; 5,661,685; 5,670,896; 5,670,897; 5,672,966; 5,673,198; 5,675,262; 5,675,270; 5,675,589; 5,677,638; 5,682,107; 5,689,133; 5,689,516; 5,691,907; 5,691,912; 5,694,047; 5,694,056; 5,724,276; 5,694,399; 5,696,454; 5,701,091; 5,701,441; 5,703,759; 5,705,932; 5,705,938; 5,708,597; 5,712,579; 5,715,197; 5,717,340; 5,719,506; 5,719,507; 5,724,276; 5,726,484; 5,726,584; 5,734,866; 5,734,868; 5,737,234; 5,737,235; 5,737,631; 5,742,178; 5,742,531; 5,744,974; 5,744,979; 5,744,995; 5,748,942; 5,748,979; 5,752,006; 5,752,035; 5,754,459; 5,758,192; 5,760,603; 5,760,604; 5,760,607; 5,761,483; 5,764,076; 5,764,534; 5,764,564; 5,768,179; 5,770,951; 5,773,993; 5,778,439; 5,781,756; 5,784,313; 5,784,577; 5,786,240; 5,787,007; 5,789,938; 5,790,479; 5,790,882; 5,795,068; 5,796,269; 5,798,656; 5,801,546; 5,801,547; 5,801,548; 5,811,985; 5,815,004; 5,815,016; 5,815,404; 5,815,405; 5,818,255; 5,818,730; 5,821,777; 5,821,774; 5,825,202; 5,825,662; 5,825,787; 5,828,230; 5,828,231; 5,828,236; 5,828,608; 5,831,448; 5,831,460; 5,831,845; 5,831,907; 5,835,402; 5,833,167; 5,838,901; 5,838,954; 5,841,296; 5,841,867; 5,844,422; 5,844,424; 5,844,829; 5,844,844; 5,847,577; 5,847,579; 5,847,580; 5,847,993; 5,852,323; 5,861,761; 5,862,082; 5,867,396; 5,870,309; 5,870,327; 5,870,586; 5,874,834; 5,875,111; 5,877,632; 5,877,7979; 5,880,492; 5,880,598; 5,880,620; 5,883,525; 5,886,538; 5,889,411; 5,889,413; 5,889,701; 5,892,681; 5,892,961; 5,894,420; 5,896,047; 5,896,329; 5,898,319; 5,898,320; 5,898,602; 5,898,618; 5,898,893; 5,907,245; 5,907,248; 5,909,125; 5,909,453; 5,910,732; 5,912,937; 5,914,514; 5,914,616; 5,920,201; 5,920,202; 5,920,223; 5,923,185; 5,923,602; 5,923,614; 5,928,338; 5,931,962; 5,933,023; 5,933,025; 5,933,369; 5,936,415; 5,936,424; 5,939,930; Re. 34,363, Re. 34,444, and Re. 34,808. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party right. Xilinx, Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx, Inc. will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

Copyright 1991-2000 Xilinx, Inc. All Rights Reserved.

### **About This Manual**

This Foundation Series 4 User Guide provides a detailed description of the Foundation™ design methodologies, design entry tools, simulation (both functional and timing simulation). Information on synthesis is included for Foundation Express users. The manual also briefly describes the Xilinx design implementation tools. Detailed descriptions of the design implementation tools can be found in two other online books, Design Manager/Flow Engine Guide and Development System Reference Guide.

Before using this manual, you should be familiar with the operations that are common to all Xilinx software tools: how to bring up the system, select a tool for use, specify operations, and manage design data. Consult the *Verilog Reference Guide* and the *VHDL Reference Guide* for detailed information on using Verilog and VHDL with Foundation Express.

### **Manual Contents**

This guide covers the following chapters:

- Chapter 1, "Introduction," lists supported architectures, platforms, and features. It also lists the available documentation and tutorials to help you get started with Foundation.

- Chapter 2, "Project Toolset," explains the two Foundation project types—Schematic Flow projects and HDL Flow projects—and how to access the various Foundation design tools from the Project Manager. It briefly describes each tool and its function.

- Chapter 3, "Design Methodologies Schematic Flow," describes various design methodologies for top-level schematic designs and state machine designs in Schematic Flow projects.

- Chapter 4, "Schematic Design Entry," explains how to manage your schematic designs and how to create hierarchical schematic designs.

- Chapter 5, "Design Methodologies HDL Flow," describes various design methodologies for HDL, schematic, and state machine designs in HDL Flow projects.

- Chapter 6, "HDL Design Entry and Synthesis," describes how to create top-level HDL designs, explains how to manage large designs, and discusses advanced design techniques.

- *Chapter 7*, "State Machine Designs," explains the basic operations for creating state machine designs.

- *Chapter 8*, "LogiBLOX," explains how to create LogiBLOX<sup>TM</sup> modules and how to use them in schematic and HDL designs.

- *Chapter 9*, "CORE Generator System" gives an overview of the Xilinx CORE Generator System.

- *Chapter 10*, "Functional Simulation," describes the basic functional simulation process.

- Chapter 11, "Design Implementation," briefly describes how to implement your design with the Xilinx Implementation Tools.

The chapter also describes how to select various design options in the Implementation Options dialog box and describes the Implementation reports.

- Chapter 12, "Verification and Programming," explains how to generate a timing-annotated netlist, how to perform a static timing analysis, and describes the basic timing simulation process. An overview of the device download tools is also included.

- Appendix A "Instantiated Components," lists the Xilinx Unified Library components most frequently instantiated in synthesis designs for FPGAs.

- "Glossary," defines some of the commonly used terms in this manual.

## **Additional Resources**

For additional information, go to http://support.xilinx.com. The following table lists some of the resources you can access from this page. You can also directly access some of these resources using the provided URLs.

| Resource             | Description/URL                                                                                                                                                                                                                                                 |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tutorial             | Tutorials covering Xilinx design flows, from design entry to verification and debugging http://support.xilinx.com/support/techsup/tutorials/index.htm                                                                                                           |

| Answers Database     | Current listing of solution records for the Xilinx software toolsSearch this database using the search function at http://support.xilinx.com/support/searchtd.htm                                                                                               |

| Application<br>Notes | Descriptions of device-specific design techniques and approaches http://support.xilinx.com/apps/appsweb.htm                                                                                                                                                     |

| Data Book            | Pages from <i>The Programmable Logic Data Book</i> , which describe device-specific information on Xilinx device characteristics, including readback, boundary scan, configuration, length count, and debugging http://support.xilinx.com/partinfo/databook.htm |

| Xcell Journals       | Quarterly journals for Xilinx programmable logic users http://support.xilinx.com/xcell/xcell.htm                                                                                                                                                                |

| Technical Tips       | Latest news, design tips, and patch information on the Xilinx design environment http://support.xilinx.com/support/techsup/journals/index.htm                                                                                                                   |

### Conventions

This manual uses the following conventions. An example illustrates each convention.

# **Typographical**

The following conventions are used for all documents.

• Courier font indicates messages, prompts, and program files that the system displays.

```

speed grade: - 100

```

• Courier bold indicates literal commands that you enter in a syntactical statement. However, braces "{}" in Courier bold are not literal and square brackets "[]" in Courier bold are literal only in the case of bus specifications, such as bus [7:0].

```

rpt del net=

```

Courier bold also indicates commands that you select from a menu.

```

File \rightarrow Open

```

- *Italic font* denotes the following items.

- Variables in a syntax statement for which you must supply values

```

edif2ngd design_name

```

References to other manuals

See the *Development System Reference Guide* for more information.

Emphasis in text

If a wire is drawn so that it overlaps the pin of a symbol, the two nets are *not* connected.

• Square brackets "[]" indicate an optional entry or parameter. However, in bus specifications, such as bus [7:0], they are required.

```

edif2ngd [option_name] design_name

```

Braces "{}" enclose a list of items from which you must choose one or more.

```

lowpwr ={on|off}

```

A vertical bar " | " separates items in a list of choices.

```

lowpwr ={on|off}

```

A vertical ellipsis indicates repetitive material that has been omitted.

```

IOB #1: Name = QOUT'

IOB #2: Name = CLKIN'

.

```

• A horizontal ellipsis "...." indicates that an item can be repeated one or more times.

```

allow block block name loc1 loc2locn;

```

### Online Document

The following conventions are used for online documents.

Red-underlined text indicates an interbook link, which is a crossreference to another book. Click the red-underlined text to open the specified cross-reference.  Blue-underlined text indicates an intrabook link, which is a crossreference within a book. Click the blue-underlined text to open the specified cross-reference.

# Chapter 1

### Introduction

This chapter contains the following sections.

- "Architecture Support"

- "Platform Support"

- "Tutorials"

- "Online Help"

- "Books"

# **Architecture Support**

The software supports the following architecture families in this release.

- XC4000E<sup>TM</sup>/L<sup>TM</sup>/EX<sup>TM</sup>/XL<sup>TM</sup>/XV<sup>TM</sup>/XLA<sup>TM</sup>

- Spartan<sup>TM</sup>/XL<sup>TM</sup>

- Spartan2™

- Virtex<sup>TM</sup>/E<sup>TM</sup>/II<sup>TM</sup>

- XC9500<sup>TM</sup>/XL<sup>TM</sup>/XV<sup>TM</sup>

The primary difference between these products lies in the number of gates and the architectural features of the individual devices.

For a detailed list of supported devices, see the "Device and Package Support" chapter in the *Foundation Series 4.1i Installation Guide and Release Notes*.

# **Platform Support**

Foundation runs on Windows NT 4.0, Windows 95, and Windows 98.

### **Tutorials**

An in-depth tutorial, the Foundation Watch Tutorial, is available from the Education tab on the Xilinx support website (http://support.xilinx.com/support/techsup/tutorials/index.htm).

# **Online Help**

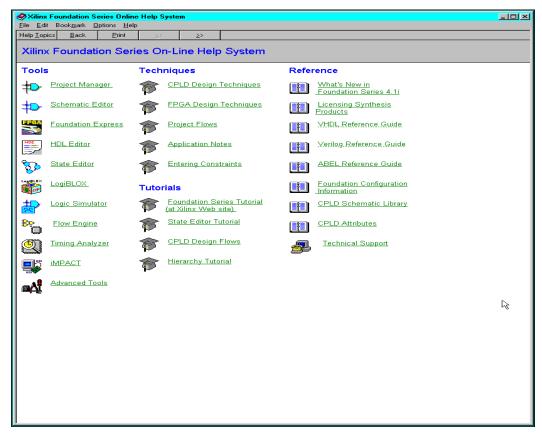

Context-sensitive online help is available for Foundation applications. In addition, Foundation includes an "umbrella" help system called the Xilinx Foundation Series On-Line Help System. The umbrella help contains topics covering all of the design entry and implementation tools provided in the product plus additional information. It also contains in-depth information essential for designing with FPGAs and CPLDs, including the following topics:

- CPLD design techniques

- FPGA design techniques

- Application notes

- Several tutorials

- Reference information on the HDL languages, CPLD schematic library and attributes, and Foundation configurations

You can invoke the "umbrella" help system (shown in the following figure) by selecting  $\mathtt{Help} \to \mathtt{Foundation} \ \mathtt{Help} \ \mathtt{Contents}$  from the Project Manager menu bar.

Figure 1-1 The Online "Umbrella" Help System

### **Books**

Multiple printed and online books are available for the Foundation Series 4 product and the various tools included with it.

### **Printed Books**

The Foundation Series 4.1i Installation Guide and Release Notes describes installation procedures, new features, supported devices, and the most critical known issues. It also includes information on the software license required for the Base Express and Foundation Express products.

Adobe Acrobat PDF files for viewing and printing all of the Foundation Series 4 online books can be found in the print directory on the Documentation CD-ROM. Refer to the *Foundation Series 4.1i Installation Guide and Release Notes* for information on accessing and printing the PDF files. Or, click Help in the Document Viewer for instructions.

#### **Online Books**

The online Foundation Series book collection is provided in both PDF and HTML.

The online Foundation Series 4 PDF collection is available from the Foundation Series 4 Documentation CD. Both PDF and HTML versions are available from the Xilinx support page on the web at http://support.xilinx.com. You must use a Java-enabled HTML browser to view the Xilinx HTML online books. If you do not already have an appropriate browser on your PC, you can install Netscape 4.0 from the Foundation Design Environment CD-ROM or the Foundation Documentation CD-ROM.

#### **Document Viewer**

The HTML Document Viewer provided with Foundation Series 4 is powered by the  $\mathsf{Docsan}^\mathsf{TM}$  indexing tool. This tool provides your HTML browser with optimal searching capabilities within the online book collection. Refer to the online help provided with the Document Viewer for detailed instructions on using this tool.

The PDF Document Viewer provided with Foundation Series 4 uses the Adobe Acrobat Viewer.

### **Foundation-Specific Online Books**

The following online books contain information that applies only to the Xilinx Foundation Series products.

| Title                             | Description                                                                                                                                                                                                                 |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Foundation Series 4 User<br>Guide | This guide provides a detailed description of the Foundation design methodologies, design entry tools, and both functional and timing simulation. The manual also briefly describes the Xilinx design implementation tools. |

| Verilog Reference Guide           | This manual describes how to use Xilinx Foundation Express to translate and optimize a Verilog description into an internal gate-level equivalent.                                                                          |

| VHDL Reference Guide              | This manual describes how to use Xilinx Foundation Express to translate and optimize a VHDL description into an internal gate-level equivalent.                                                                             |

### **Design Entry Online Reference Books**

The following books contain additional information not found in the Foundation-specific books regarding the Xilinx schematic library components (and constraints) and LogiBLOX.

| Title           | Description                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Libraries Guide | This book describes the logic elements (primitives or macros), that you use to create your designs as well as the attributes and constraints used to process elements during logic implementation. It also discusses relationally placed macros (RPMs), which are macros that contain relative location constraints (RLOC) information. The Xilinx libraries enable you to convert designs easily from one family to another. |

| Title             | Description                                                                                                                                                                                                                                                                                                          |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Constraints Guide | This book provides a detailed description of each Xilinx constraint. Descriptions include supported architectures for each constraint, applicable elements, propagation rules and syntax examples of constraints entry methods.                                                                                      |

| LogiBLOX Guide    | This guide describes the high-level modules you can use to speed up design entry and the attributes that support logic synthesis, primarily for FPGA architectures. It also explains how to use the LogiBLOX program to create designs and the different types of logic synthesis completed by the LogiBLOX program. |

**Note** The CORE Generator User Guide is not currently part of the online book collection. It is an Adobe Acrobat file (.pdf) that can be accessed from the CORE Generator Help menu ( $\mathtt{Help} \rightarrow \mathtt{Online}$  Documentation.)

### **Synthesis and Simulation Reference Book**

The following book contains general information on Synthesis and Simulation.

| Title                                    | Description                                                                                                                                                                                                                             |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Synthesis and Simulation<br>Design Guide | This manual provides a general overview of designing FPGAs with Hardware Description Languages (HDLs). It includes design hints for the novice HDL user, as well as for the experienced user who is designing FPGAs for the first time. |

### Implementation-Related Online Books

The following books contain detailed information on the Xilinx implementation tools. Much of the information contained in these books is for the standalone or command line versions of the tool.

| Title                                | Description                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Constraints Editor Guide             | This manual describes the Xilinx Constraints Editor GUI that can be used <i>after</i> the design has been implemented to modify or delete existing constraints or add new constraints to a design.                                                                                                                                                                                                           |

| Design Manager/<br>Flow Engine Guide | This manual describes the Design Manager, a Xilinx Alliance Series tool for managing multiple implementations of the same design. This manual also explains the Xilinx Flow Engine, which implements designs, and explains how to interact with other programs that run in the Design Manager environment; namely, the Design Editor, the Timing Analyzer, the PROM File Formatter, and the PROM Programmer. |

| Development System Reference Guide   | This book describes the Xilinx design implementation software, which includes programs to generate EDIF files, LCA files, and BIT files. The book covers all the program options and files that are generated by these programs. It also contains in-depth information on timing constraints.                                                                                                                |

| FPGA Editor Guide                    | The FPGA Editor is a graphical editor used to display and configure FPGAs. The FPGA Editor enables you to place and route critical components before running automatic place and route tools on an entire design, modify placement and routing manually, interact with the physical constraints file (PCF) to create and modify constraints, and verify timing against constraints.                          |

| Floorplanner Guide                   | This book describes the Floorplanner, a graphical interface tool to help you improve performance and density of your design.                                                                                                                                                                                                                                                                                 |

| Timing Analyzer Guide                | This manual describes Xilinx's Timing Analyzer program, a graphical user interface tool that performs static analysis of a mapped FPGA or CPLD design. The mapped design can be partially or completely placed, routed, or both.                                                                                                                                                                             |

### **Device Programming Online Books**

Detailed information on the device programming process is included in the following books.

| Title                     | Description                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| iMPACT User Guide         | This guide documents the graphical interface used for insystem programming and verification of CPLD and FPGA parts.                                                                                                                                                                                                                                                                                 |

| PROM File Formatter Guide | (FPGAs only) This manual explains how to use a Windows-<br>based tool to format bitstream files into HEX format files<br>compatible with Xilinx and third-party PROM program-<br>mers. You use the PROM files to program a PROM device,<br>which is then used to configure daisy chains of one or more<br>FPGAs for one application (configuration) or several appli-<br>cations (reconfiguration). |

# **Project Toolset**

This chapter explains how to create Foundation projects and how to access the various Foundation tools that you use to complete the project. Each tool and its function is briefly described. This chapter contains the following sections.

- "Creating Foundation 4 Projects"

- "Project Manager"

- "Accessing LogiBLOX"

- "Accessing the CORE Generator System"

- "Documenting Your Design"

- "Project Archiving"

- "Design Entry Tools"

- · "Synthesis Tools"

- "Simulation/Verification"

- "Constraints Editors"

- "Implementation Tools"

- "Device Programming"

- "Utilities"

# **Creating Foundation 4 Projects**

To organize your work, Foundation groups all related files into separate logical units called projects. Schematic, HDL, and Finite State Machine (FSM) designs must be defined as elements in a project. The associated libraries as well as netlists, bitstream files, reports, and configuration files are all part of the project.

Each project is stored in a separate directory called the project working directory. The location of the project working directory is specified when the project is created. The name of the project working directory is the same as the name of the project.

A Foundation Series 4 project can be either a Schematic Flow project or an HDL Flow project. If you are using the Base (DS-FND-BAS-PC) or Standard (DS-FND-STD-PC) products, only the Schematic Flow is available to you. Both flows are available to Base Express (DS-FND-BSX-PC) and Foundation Express (DS-FND-EXP-PC) users.

### **Schematic Flow Projects**

A Schematic Flow project can have top-level schematic or ABEL files. Top-level schematic designs can contain underlying schematic, Logi-BLOX, CORE Generator, or ABEL macros. The top-level ABEL files or underlying ABEL macros can be created with the Finite State Machine (FSM) Editor or a text editor. (Top-level ABEL files are not recommended for FPGA projects.)

If you have Base Express or Foundation Express, a Schematic Flow project can also have underlying HDL, VHDL, or ABEL macros created with the HDL Editor. FSM Editor. or another text editor.

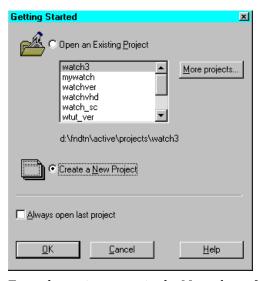

To create a Schematic Flow project, perform the following steps.

Open the Project Manager by clicking on the Project Manager icon (shown below) on your desktop or by Start →

Programs→ Xilinx Foundation Series 4 → Project Manager.

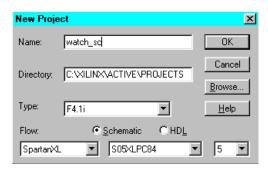

2. Click the Create a New Project radio button on the Getting Started dialog box. Click OK. (To create new projects, you can also select File  $\rightarrow$  New Project from the Project Manager.)

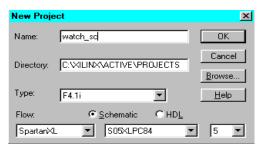

- 3. Enter the project name, up to 8 characters, in the Name field of the New Project dialog box.

- 4. Select a location for the project in the Directory box.

- 5. Select **F4.1i** as the project type in the Type box.

- 6. Select the Schematic Flow.

- 7. Enter the device family, part, and speed of your target device.

#### 8. Click ok.

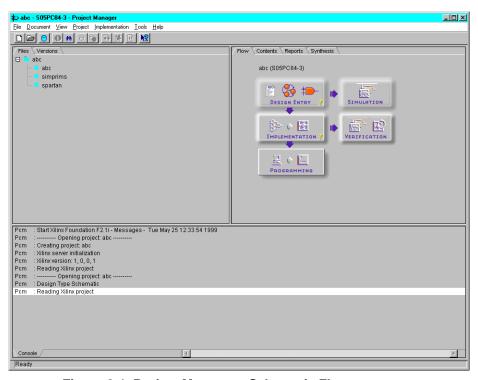

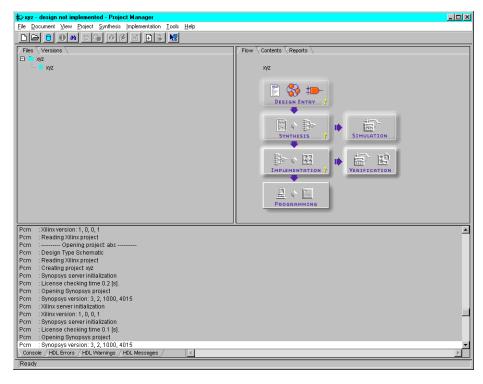

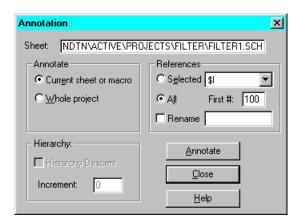

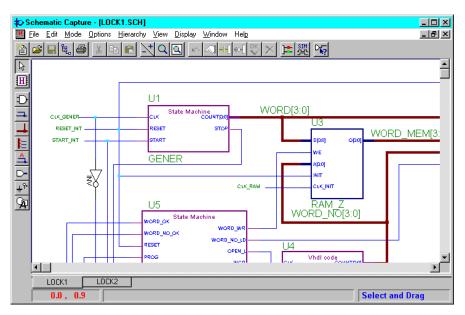

The Project Manager screen for the new project appears (see Figure 2-1). The Project Manager screen contains three main sections.

- On the left side is the Hierarchy Browser consisting of a hierarchy tree of the project files on the Files tab and of the project implementation versions on the Versions tab.

- The upper right area includes the Flow tab showing the design flowchart with the functions used for Schematic Flow projects. This section also contains Contents, Reports, and Synthesis tabs. If you create any lower-level HDL or FSM macros for the project, you can use functions on the Synthesis tab to list and update them. From the Contents tab, you can view information on the Files shown in the Hierarchy Browser area. You can access system-created reports from the Reports tab.

- The bottom console area displays errors, warnings, and messages.

Refer to the "Project Manager" section later in this chapter for more information on the Project Manager and the tools accessed from it.

Figure 2-1 Project Manager - Schematic Flow

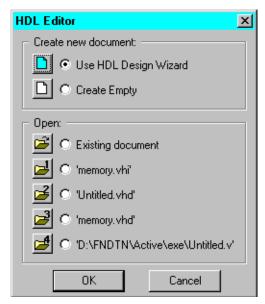

### **HDL Flow Projects (Express Only)**

An HDL Flow project can contain VHDL, Verilog, or schematic toplevel designs with underlying VHDL, Verilog, or schematic modules. HDL files can be created by the HDL Editor, Finite State Machine Editor, or other text editors.

LogiBLOX, CORE Generator, and ABEL modules as well as XNF files can be instantiated in the VHDL and Verilog code using the "black box instantiation" method.

To create an HDL Flow project, perform the following steps.

Open the Project Manager by clicking on the Project Manager icon (shown below) or by Start → Programs→ Xilinx Foundation Series 4 → Project Manager.

2. Click the Create a New Project radio button on the Getting Started dialog box. Click OK. (To create new projects, you can also select File  $\rightarrow$  New Project from the Project Manager.)

3. Enter the project name in the Name box of the New Project dialog.

- 4. Select a location for the project in the Directory box.

- Select F4.1i as the project type in the Type box.

- 6. Select the **HDL** Flow.

**Note** When you select the HDL Flow button, the device family, part, and speed boxes for the target device are removed. You do not need to select a target device for HDL Flow projects until the design is synthesized.

#### 7. Click or.

The Project Manager screen for the new project appears. The Project Manager screen contains three sections.

- On the left side is the Hierarchy Browser consisting of a hierarchy tree of the project files on the Files tab and of the project versions on the Versions tab.

- The upper right area includes the Flow tab showing the design flowchart with the functions used for HDL Flow projects. This section also contains Contents and Reports tabs. From the Contents tab, you can view information on the Files and Versions shown in the Hierarchy Browser area. You can access system-created reports from the Reports tab.

- The bottom Console tab displays errors, warnings, and messages. The HDL Errors, HDL Warnings, and HDL Messages tabs display information about synthesis results when a specific version of the project is selected.

Refer to the "Project Manager" section later in this chapter for more information on the Project Manager and the tools accessed from it.

Figure 2-2 Project Manager - HDL Flow

# **Project Manager**

The Project Manager, the overall project management tool, contains the Foundation Series tools used in the design process. Figure 2-1 and Figure 2-2 illustrate the tools accessible for the two Foundation 4 project flow types. It is through the Project Manager that you access the tools for the design process from design entry tools to device programming.

The Project Manager performs the following functions:

- Automatically loads all design resources when opening a project

- Checks that all project resources are available and up-to-date

- Illustrates the design process flow

- Initiates applications used in the design process

- Displays error and status messages in the message window

- Provides automated data transfer between various Foundation design tools

- Displays design status information

The three main regions of the Project Manager are discussed in the following sections

### **Hierarchy Browser**

Foundation organizes related files into a distinct logical unit called a *project*. Related files include the following:

- Project documents (schematics, HDL source files, and state diagram files)

- Project libraries

- Output and intermediate files (netlists, bitstreams, report and log files)

- Configuration files

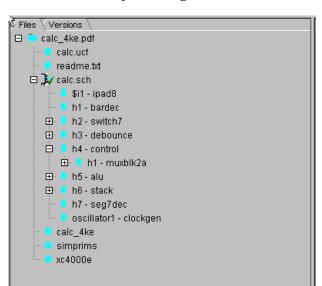

Two tabs in the Hierarchy Browser area on the Project Manager window keep track of these files. The Hierarchy Browser is an interactive area in addition to a display area. You can open the listed files and versions/revisions by double clicking on them in the Hierarchy Browser—the application that is associated with the file type is invoked. For example, if you double click on a schematic file, the Schematic Editor displays the schematic file. You can also access menus listing the functions you can perform on the displayed items by right clicking on the item.

The Hierarchy Browser's Files and Version tabs are summarized in the following sections. To learn more about how to use the hierarchy browser, select  $\texttt{Help} \rightarrow \texttt{Foundation}$  Help  $\texttt{Contents} \rightarrow \texttt{Project}$   $\texttt{Manager} \rightarrow \texttt{Hierarchy}$  Browser.

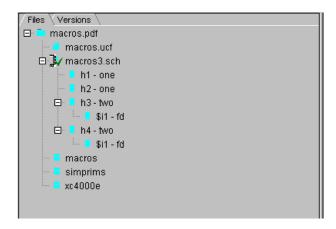

#### Files Tab

The Files tab displays the hierarchy of the project files, project libraries, and external files. From this tab you can add, remove, or reorder the displayed files and libraries as well as open applications associated with them.

For new projects, the Project Manager automatically creates the following files:

- A configuration file called the Project Description File (PDF). The PDF file has the same name as the project plus the .pdf extension. The PDF file is stored at the top-level of the associated project directory.

- Three types of library files (project library, Simprims library, and device library). In HDL Flow projects, the Simprims library and device library are not added until the device is selected in the Synthesis phase.

A Foundation project always has one or more "top-level" design file(s). In a Schematic Flow project, you can see what the top-level designs in the project are by looking at the top level of the Hierarchy Browser. In a Schematic Flow project, all top-level files must be schematics, FSM (ABEL) diagrams, or ABEL files. In an HDL Flow project, you designate the top-level entity or module at the time of synthesis. The list of entities/modules is automatically generated from the list of HDL source files that have been added to the project. The added HDL design files are displayed in the File tab of the Hierarchy Browser and can be VHDL, Verilog, or schematic files.

The following table shows some the of common project files included in the Hierarchy Browser, their extensions, and the Foundation tool that creates them.

| Extension | File Type                        | Created By        |

|-----------|----------------------------------|-------------------|

| .pdf      | Project description file         | Project Manager   |

| .sch      | Schematic source file            | Schematic Capture |

| .v        | Verilog source file              | HDL Editor        |

| .vhd      | VHDL source file                 | HDL Editor        |

| .abl      | ABEL source file                 | HDL Editor        |

| .asf      | Finite State Machine source file | FSM Editor        |

| Extension | File Type             | Created By                |

|-----------|-----------------------|---------------------------|

| .ucf      | User constraints file | <b>Constraints Editor</b> |

| .tve      | Test vector file      | Logic Simulator           |

For detailed information about the project files, libraries, and other project information, refer to the online help by selecting  $\mathtt{Help} \rightarrow \mathtt{Foundation}$  Help Contents $\rightarrow \mathtt{Foundation}$  Configuration Information.

#### **Versions Tab**

The Versions tab displays the revisions and versions of the chip implementations of the design. For a newly created project, this tab is empty.

Project management consists of control over design versions and revisions. A version represents an input design netlist. Each time a change is made to the source design, such as logic being added to or removed from the schematic or the HDL source being modified, a new version may be created. A revision represents an implementation on a given version, usually with new implementation options such as different placement or router effort level.

### **Project Flowchart Area**

The Foundation 4 Project Manager's project flowchart area contains four tabs that allow you to obtain current information about your current project and facilitate the design process.

### Flow Tab - Project Flowchart

The Flow tab displays the project flowchart. You use the buttons on the flowchart to perform steps in the design flow, from design entry through device programming. The buttons included in the flowchart in this area depend on whether you have a Schematic Flow project or an HDL Flow project (see Figure 2-1 and Figure 2-2).

When you start programs from the project flowchart, the Project Manager automatically controls the transfer of input and output data (files) between the applications. It performs the necessary steps to take the design to the point you requested.

#### Alternatives to Flowchart Buttons

In addition to the project flowchart, the Project Manager includes a number of alternative ways to run the Foundation application tools. You can access tools by right-clicking items listed in the Hierarchy Browser area. Or, you can use the Tools menus in the Project Manager Toolbar to access submenus for Design Entry, Simulation/Verification, Implementation, and Device Programming tools. It is also possible to start the Foundation applications directly from the Windows environment. The latter method is not recommended because, depending on the application, the Project Manager may not be started and would not be available to track the project properly.

#### Contents Tab

The Contents tab displays info related to the object currently selected (file, library, etc.) from the hierarchy tree on the Files tab. It displays the full pathname of the object selected as well as the date the object was last modified.

### Reports Tab

Select this tab to access and display reports that have been generated in the design process.

### Synthesis Tab (Schematic Flow Only)

Using the Synthesis tab, you can update or synthesize VHDL, Verilog, ABEL, and State Machine macros. Refer to the "Synthesis Tools" section later is this chapter for more information on this tab. (This tab is unnecessary in an HDL Flow project because the entire project is synthesized.)

### **Messages Area**

The tabs included in the Messages area display general project messages and specific HDL processing messages.

#### Console Tab

The Console tab displays the contents of the project log.

### **HDL Errors Tab (HDL Flow Only)**

This tab displays any errors encountered during HDL source file analysis, for the object selected in the Hierarchy Browser.

### **HDL Warnings Tab (HDL Flow Only)**

This tab displays warnings generated during HDL source file processing, for the object selected in the Hierarchy Browser.

### **HDL Messages Tab (HDL Flow Only)**

This tab displays messages other than errors or warnings generated during HDL source file processing, for the object selected in the Hierarchy Browser.

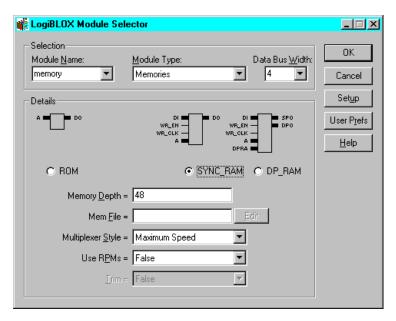

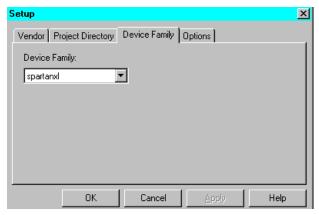

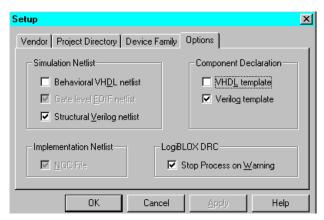

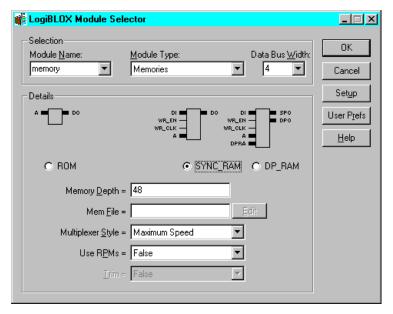

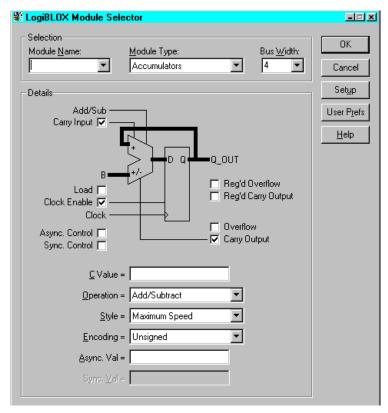

# **Accessing LogiBLOX**

LogiBLOX is a graphical interactive tool for creating high-level modules, such as counters, shift registers, and multiplexers. Logi-BLOX includes both a library of generic modules and a set of tools for customizing them. You can access LogiBLOX from the Project Manager by selecting Tools  $\rightarrow$  Design Entry  $\rightarrow$  LogiBLOX module generator, from the Schematic Editor by selecting Tools  $\rightarrow$  LogiBLOX module generator or from the HDL Editor by selecting Tools  $\rightarrow$  LogiBLOX. For details about creating LogiBLOX modules, refer to the "Creating LogiBLOX Modules" section of the "LogiBLOX" chapter.

**Note** LogiBLOX supports all Xilinx architectures except Virtex.

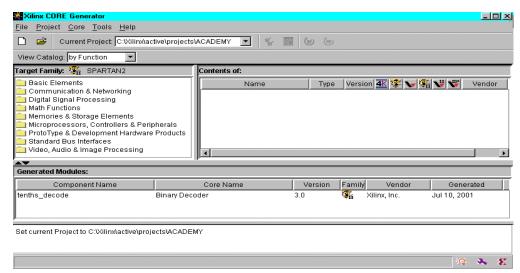

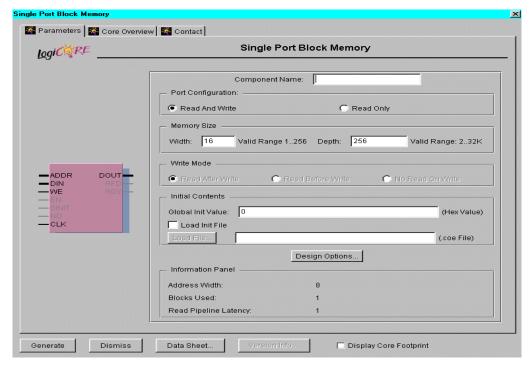

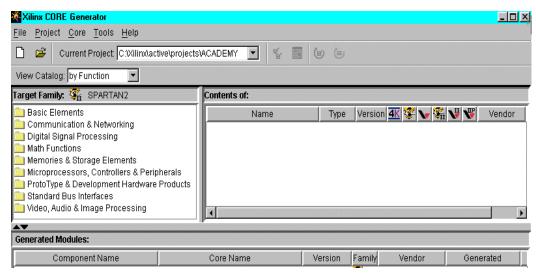

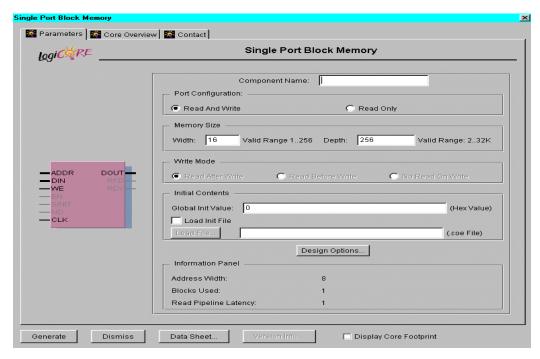

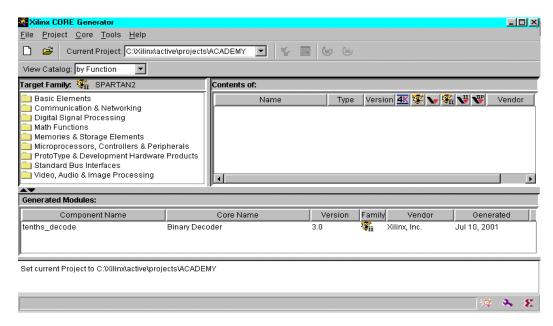

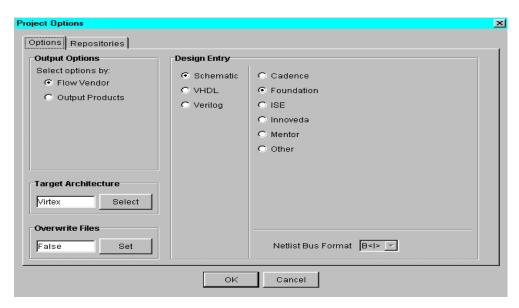

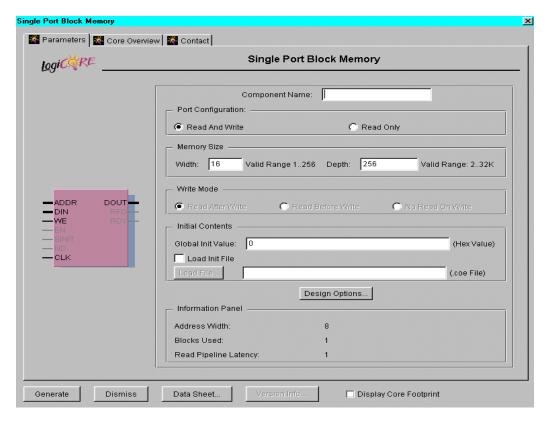

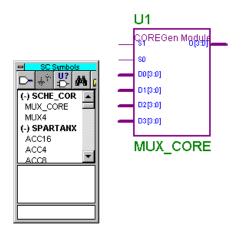

# **Accessing the CORE Generator System**

The Xilinx CORE Generator is a graphical interactive tool that generates and delivers parameterizable cores optimized for Xilinx FPGAs. You can access the CORE Generator system from the Project Manager by selecting  $\mathtt{Tools} \rightarrow \mathtt{Design} \ \mathtt{Entry} \rightarrow \mathtt{CORE} \ \mathtt{Generator}$  or from the Schematic Editor or HDL Editor by selecting  $\mathtt{Tools} \rightarrow \mathtt{CORE} \ \mathtt{Generator}$ . For more information on the CORE Generator system, refer to the CORE Generator online help.

# **Documenting Your Design**

To attach text files or other files to the Project, perform the following steps.

- 1. Select Document  $\rightarrow$  Add.

- In the Add Document dialog box, select the documents from the Files list box.

- Click ok.

The files are then displayed in the Hierarchy Browser area. This is a convenient way to provide documentation for your design. Note that you can add almost any kind of file to the project.

# **Project Archiving**

Foundation 4 supports automatic project archiving. Any or all of the following project components: project files, design source files, synthesis files, implementation files, or documentation files can be zipped into a single file or into multiple files. When you select File  $\rightarrow$  Archive Project from the Project Manager, the Archive Project Wizard - Setup window appears. In this window, you can specify the location for the archive .zip file, add comments, provide a password, or modify the compression factor. A second window, the Project Components window, allows you to select the parts of the project to be archived. Likewise, the Foundation Project Manager contains a Restore Project option to automatically unzip archived projects. (File  $\rightarrow$  Restore Project).

Project archiving maintains revision control. The resultant files from each implementation revision are archived in the project directory. The source design for each version is *not* archived, only the resulting netlists and files for each revision. Therefore, if you want to save iterations of the source design (schematics, HDL files, for example), you must back those up yourself.

Foundation 4 also supports archiving of symbol libraries as well as any other user files (release notes, application notes, etc.) you want to save. To archive symbol libraries or other user files, perform the following steps:

- 1. Select File ightarrow Archive Project.

- 2. Select **Next** from the Archive Project Wizard Setup window.

- Select Next from the Project Components window to display the User Files window.

- 4. Select Add Libraries and then select the libraries from the list box that you want to archive. Or, select Add Files to select any additional files to archive.

- 5. Select Start to begin archiving.

# **Design Entry Tools**

This section describes the design entry tools. Foundation includes a suite of tools for creating digital circuit designs. These tools provide the following design entry capabilities.

- Top-level schematic entry with the Xilinx Unified libraries components, LogiBLOX symbols, CORE Generator modules, HDL macros, and State Machine macros

- Top-level HDL design entry and synthesis

- Top-level HDL designs with state machine, CORE Generator, or LogiBLOX instantiated components

- Finite state machine diagram entry

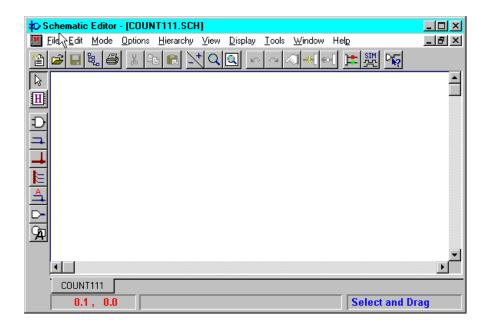

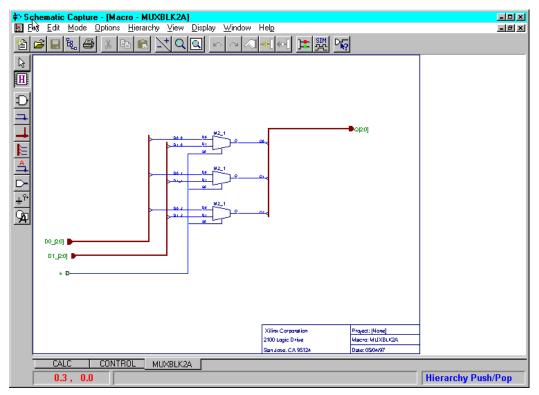

### **Schematic Editor**

With the Schematic Editor, you can create multi-sheet hierarchical schematics. The editor features include the following.

- Multiple sheet and hierarchical schematic support

- Viewlogic schematic import

- Board-level and PLD schematic support (requires the Active-CAD tool)

- Export of schematic netlists to XNF, EDIF, VHDL, and Verilog formats

- Integration with synthesis design tools (HDL Editor and State Diagram editor)

- Integration with the Logic Simulator

For detailed information about the Schematic Editor, select  $\texttt{Help} \rightarrow \texttt{Foundation Help Contents} \rightarrow \texttt{Schematic Editor}$ . Also, see the "Schematic Design Entry" chapter.

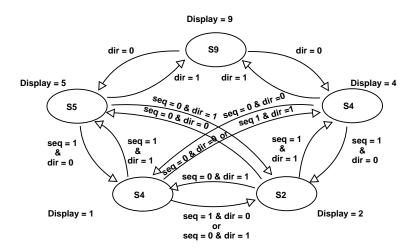

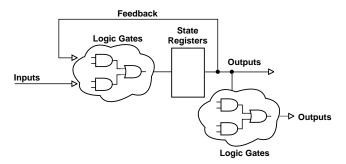

#### **State Editor**

State machine designs typically start with the translation of a concept into a "paper design," usually in the form of a state diagram or a bubble diagram. The paper design is converted to a state table and finally into the source code itself. The State Editor, which allows you to create state machine designs, also supports the following functions:

- Generates behavioral VHDL, Verilog, or ABEL (Schematic Flow only) code from the state diagram

- Invokes the Express or XABEL compiler to convert the behavioral description into a gate-level netlist

- Simulates a state diagram macro graphically

For more information about how to use the State Editor, select  $Help \rightarrow Foundation Help Contents \rightarrow State Editor.$

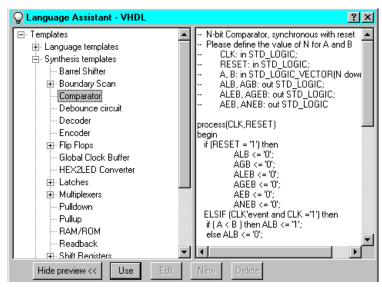

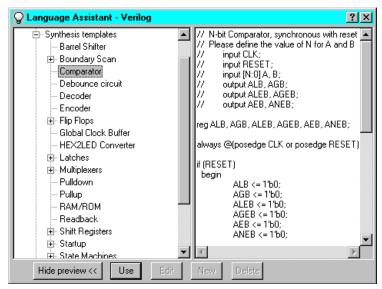

#### **HDL Editor**

The HDL Editor, a text editor, is designed to edit HDL source files created in the VHDL, Verilog, or ABEL (Schematic Flow only) languages. The HDL Editor utilizes syntax coloring for the VHDL, Verilog, and ABEL languages. The HDL Editor allows you to check HDL language syntax as well as create HDL macro symbols for placement on a schematic.

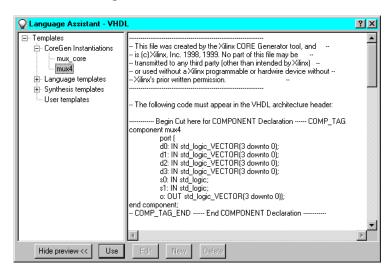

The Language Assistant tool (Tools  $\rightarrow$  Language Assistant in the HDL Editor) furnishes the following templates with source code for VHDL, Verilog, and ABEL.

- · Language templates with basic language constructs

- Synthesis templates of functional blocks such as counters, flipflops, multiplexers, and Xilinx architectural features such as Boundary Scan and RAM

For detailed information about the HDL Editor, select  $\mathtt{Help} \to \mathtt{Foundation}$  Help Contents  $\to \mathtt{HDL}$  Editor. Also, refer to the "HDL Design Entry and Synthesis" chapter.

### **Symbol Editor**

With the Symbol Editor, you can edit features of component symbols such as pin locations, pin names, pin numbers, pin shape, and pin descriptions.

From the Project Manager, you can access the Symbol Editor by selecting Tools  $\rightarrow$  Design Entry  $\rightarrow$  Symbol Editor.

For more details on how to use the Symbol Editor, select  $\mathtt{Help} \to \mathtt{Foundation} \ \mathtt{Help} \ \mathtt{Contents} \to \mathtt{Advanced} \ \mathtt{Tools} \to \mathtt{Symbol} \ \mathtt{Editor}.$

# Synthesis Tools

Synthesis tools are available for both HDL Flow projects and Schematic Flow projects. If you are using the Base or Standard product, synthesis tools are available for Finite State Machine ABEL macros only.

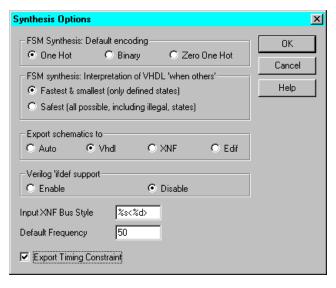

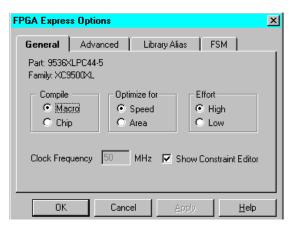

### Synthesis Button (HDL Flow)

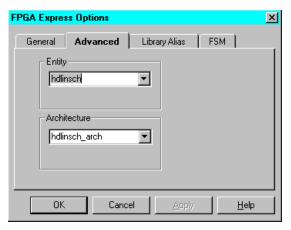

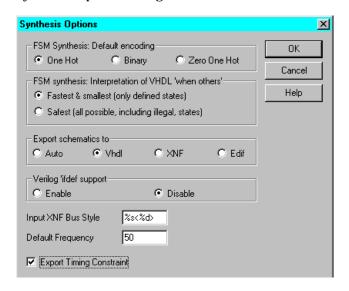

For design synthesis, Base Express and Foundation Express users have access to FPGA Express from Synopsys, the industry-leading synthesis technology. The Express synthesis tools provide the following capabilities.

- Architecture-specific optimization

- Verilog, VHDL, or mixed HDL synthesis

- Automatic Finite State Machine extraction

- Automatic GSR and I/O insertion

- Graphical constraints editor. The Express Constraints Editor GUI is available to Foundation Express users only. It is used to set design constraints and view estimated design performance.

### Synthesis Tab (Schematic Flow)

In a Schematic Flow project, the necessary synthesis of any underlying HDL macros in the design can be initiated in the various design entry tools. The Synthesis tab provides the capability to synthesize any or all of the HDL macros (FSM, ABEL, VHDL, or Verilog) in the current project and update the macro symbol and netlist without

searching manually through the project and synthesizing/updating them individually.

#### Simulation/Verification

Simulation and verification tools are available for both Schematic and HDL Flow projects to determine if the timing requirements and functionality of your design have been met.

## **Logic Simulator**

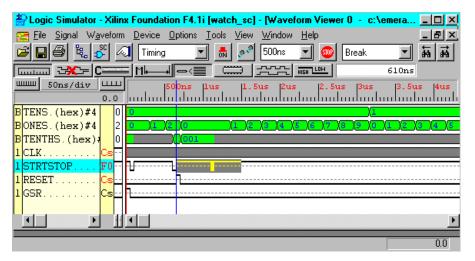

The Logic Simulator is a real-time interactive design tool for both functional and timing simulation of designs. You access the Logic Simulator from the project flowchart when you click the Simulation button or the Timing Simulation icon on the Verification button.

The Logic Simulator creates an electronic breadboard of your design directly from your design's netlist. The breadboard is tested with signals called test vectors. Each test vector lists logical states of all stimulus signals at a selected time interval. See the "Functional Simulation" chapter and the "Verification and Programming" chapter for more information on simulations. For details on how to use the Logic Simulator, select  $\mathtt{Help} \to \mathtt{Foundation}$   $\mathtt{Help}$   $\mathtt{Contents} \to \mathtt{Logic}$   $\mathtt{Simulator}$ .

## **Timing Analyzer**

Select the Timing Analyzer icon on the Verification button on the project flowchart to access the Timing Analyzer for verification based on the post-layout timing netlist. The Timing Analyzer is used to verify that the delay along a given path or paths meets your specified timing requirements. It creates timing analysis reports that you customize by applying filters. It organizes and displays data that allows you to analyze the critical paths in your circuit, the cycle time of the circuit, the delay along any specified paths, and the paths with the greatest delay. It also provide a quick analysis of the effect of different speed grades on the same design.

## **Specialized Simulation Controls**

Typically, the Simulation and Verification functions are invoked from the project flowchart buttons. You can access the following individual functions from the Project Manager toolbar, if needed.

Gate Simulator

When you select  $\mathtt{Tools} \rightarrow \mathtt{Simulation/Verification} \rightarrow \mathtt{Gate}$  Simulator from the Project Manager toolbar, you access three startup options for the simulator.

- Opening the simulator with the netlist from the currently open Foundation project

- Selecting the netlist manually

- Opening the simulator without loading a netlist

- Checkpoint Gate Simulation Control

Checkpoint simulation pulls simulation data from the current stage of the design database. If you want to select which netlist (hierarchical or flat NGA netlist) to use for timing simulation, you can access the Checkpoint Gate Simulation Control dialog by selecting Tools  $\rightarrow$  Simulation/Verification  $\rightarrow$  Checkpoint Gate Simulation Control on the Project Manager toolbar.

## **HDL Behavioral Simulation Capabilities**

Foundation Series 4 allows you to add HDL behavioral simulation capabilities to all design flows. HDL simulators from Aldec, Incorporated, and from MTI can be added to your Xilinx software. Sale and support for Aldec's ACTIVE-VHDL Behavioral Simulator and for MTI's ModelSim product are handled directly by those vendors.

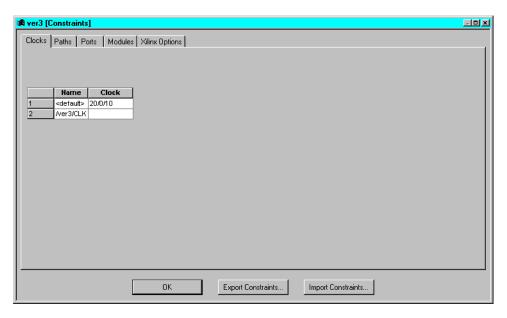

#### **Constraints Editors**

Two Constraints Editor GUIs are available in Foundation to assist with constraining elements of your design to obtain the desired performance.

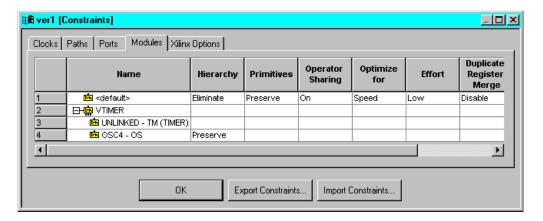

## **Express Constraints Editor (HDL Flow)**

The Express Constraints Editor is a feature available in the Foundation Express product only. The Express Constraints Editor is a GUI that allows you to set performance constraints, attributes, and optimization controls in the Synthesis phase before you start to optimize a design. Constraint entry is in the form of constraints tables for logically related groups (clocks, ports, paths, modules). Design-specific information based on the architecture specified for the selected version of the design is automatically extracted and displayed in the tables.

#### **Xilinx Constraints Editor**

The Xilinx Constraints Editor GUI allows you to create and edit certain constraints after the translation step in the Implementation phase of the design without directly editing the UCF (User Constraint File).

You can start the Constraints Editor from the Project Manager by selecting Tools  $\rightarrow$  Implementation  $\rightarrow$  Constraints Editor.

You can also invoke the Xilinx Constraints Editor by selecting Start  $\rightarrow$  Programs  $\rightarrow$  Xilinx Foundation Series 4  $\rightarrow$  Accessories  $\rightarrow$  Constraints Editor.

The Xilinx Constraints Editor is not the same as the Express Constraints Editor available in the HDL Flow and is most useful for schematic and ABEL designs in Schematic Flow projects.

For more on the Constraints Editor, refer to the *Constraints Editor Guide*, an online book.

# **Implementation Tools**

Once you have completed design entry and are ready for physical implementation of the design, you begin implementation processing by clicking the Implementation button on the project flowchart. All the steps needed to obtain the final results are invoked automatically. Refer to the "Design Implementation" chapter for more information.

#### **Control Files**

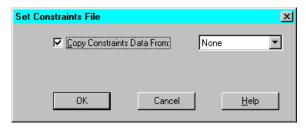

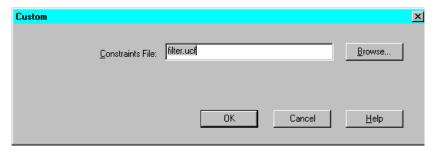

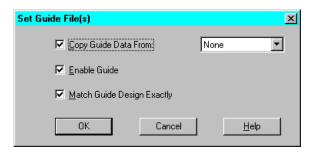

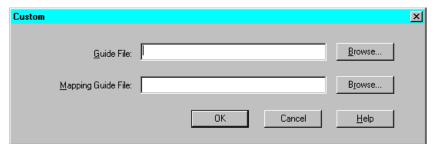

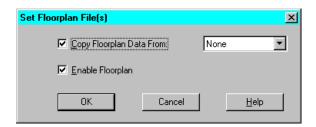

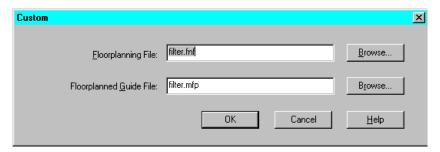

You can control the implementation of your design with a user constraints file, an implementation guide file, or a Floorplanner file. You can set these files by selecting Implementation → Set Guide File(s), or Set Floorplan File(s), or Set Constraints File(s) from the Project Manager. Or, you can access a dialog box to set the files by clicking the Control Files SET button in the Physical Implementation Settings section of the window that appears when you implement a new version or revision of your design.

#### **User Constraints File**

Constraints can be applied to control the implementation of a design. Location constraints, for example, can be used to control the mapping and positioning of logic elements in the target device. Timing constraints can be used to identify critical paths that need closer placement and faster routing. For a list of the constraints that can be applied for the various devices, refer to the *Constraints Guide*.

The User Constraints File (UCF) is a user-created ASCII file that holds the constraints. You can enter the constraints directly in the input design. However, putting them in the UCF separates them from the input design files and provides for easier modification and reduces re-synthesis of your design. You can create the UCF using a text editor or you can use the Xilinx Constraints Editor to produce the UCF for you. UCF files can also be reused from design to design.

#### Implementation Guide File

Guide files from a previous implementation can be used to speed up the current implementation. When an implementation guide file is specified, only the sections of the current revision that are different from the specified guide file for the previous revision are processed.

#### Floorplanner File

The Floorplanner tool generates an MFP file that contains mapping and placement information. You can use this file as a guide for mapping an implementation revision for the XC4000, Spartan, and Virtex device families only. For Floorplanner guide files information, refer to the *Floorplanner Guide*, an online manual.

## **Implementation Tools Menu**

Typically, designs are implemented by using the Implementation button on the project flowchart. However, you can access certain specialized functions from the Project Manager Tools menu.

#### **Constraints Editor**

The Constraints Editor accessed from the Project Manager by selecting  $\mathtt{Tools} \to \mathtt{Implementation} \to \mathtt{Constraints}$  Editor is the Xilinx Constraints Editor. It becomes available for design implementation after the translation step in Flow Engine has completed. For more on the Constraints Editor, refer to the *Constraints Editor Guide*, an online book.

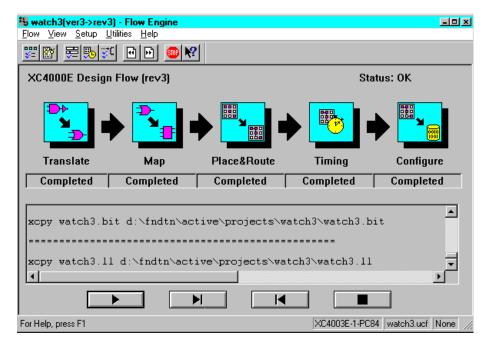

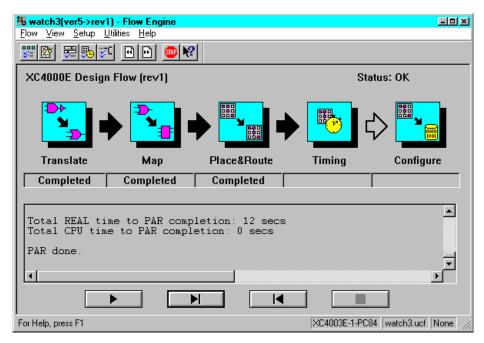

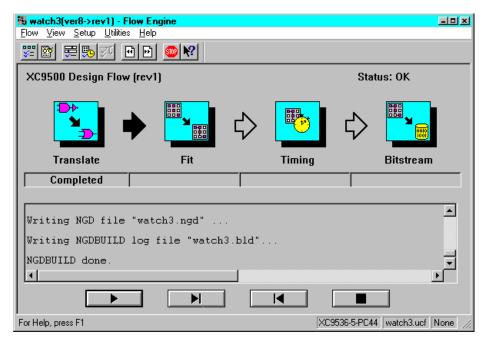

#### Flow Engine

The Flow Engine processes the design, controls the implementation of the design, and guides the implementation revisions. When initiated by selecting Tools → Implementation → Flow Engine, the Flow Engine is run as a standalone program. The project is not automatically brought up-to-date as it is when initiated by the Implementation button on the project flowchart. For more information, see the "Implementing a Design" section of the "Design Implementation" chapter.

#### Floorplanner

Selecting Tools  $\rightarrow$  Implementation  $\rightarrow$  Floor Planner from the Project Manager window, accesses the Floorplanner tool (for FPGAs only). The Floorplanner creates a file that contains mapping information, which can be used by the Flow Engine as a guide for mapping an FPGA implementation revision. For more information on the Floorplanner, see the *Floorplanner Guide*, an online book.

#### **FPGA Editor**

Selecting **Tools**  $\rightarrow$  **Implementation**  $\rightarrow$  **FPGA Editor** from the Project Manager window opens the FPGA Editor. The FPGA Editor provides a graphic view of your placed and routed design, allowing you to make modifications. This option is supported for FPGAs only.

For more information on using the FPGA Editor, see the *FPGA Editor Guide*, an online book.

#### **CPLD ChipViewer**

Selecting Tools  $\rightarrow$  Implementation  $\rightarrow$  CPLD ChipViewer from the Project Manager window opens the ChipViewer. The ChipViewer provides a graphical view of the CPLD fitting report. With this tool you can examine inputs and outputs, macrocell details, equations, and pin assignments. You can examine both pre-fitting and post-fitting results.

More information on using the CPLD ChipViewer is available in that tool's online help or from the Umbrella Help menu accessed by  $\texttt{Help} \rightarrow \texttt{Foundation Help Contents} \rightarrow \texttt{Advanced Tools} \rightarrow \texttt{ChipViewer}.$

#### **Automatic Pin Locking**

I/O pins can be locked to a previous revision by clicking on the revision in the Versions tab of the Project Manger and selecting Tools → Implementation → Lock Device Pins. The Lock Pins Status dialog appears upon completion. You can click View Lock Pins Report from the Lock Pin Status dialog or select Tools → Implementation → View Locked Pins Report to access the Lock Pins Report. The Lock Pins Report contains information on any constraint conflicts between the pin locking constraints in the existing UCF file and the design file.

# **Device Programming**

When the design meets your requirements, the last step in its processing is programming the target device. To initiate this step, click the Programming button in the project flowchart. The Select Programming dialog appears listing one or more of the following device programming tools: iMPACT and PROM File Formatter.

#### **IMPACT**

The iMPACT tool downloads, reads back, and verifies FPGA and CPLD design configuration data. It can also perform functional tests on any device and probe the internal logic states of your design.

#### **PROM File Formatter**

The PROM File Formatter is available for FPGA designs only. The PROM File Formatter provides a graphical user interface that allows you to do the following.

- Format BIT files into a PROM file compatible with Xilinx and third-party PROM programmers

- Concatenate multiple bitstreams into a single PROM file for daisy chain applications

- Store several applications in the same PROM file

#### **Utilities**

Foundation contains multiple utilities to help you manage and organize your project. Those available from the Project Manager's Tools

— Utilities menu are described below.

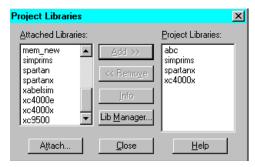

## **Schematic Symbol Library Manager**

The Library Manager allows you to perform a variety of operations on the design entry tools libraries and their contents, such as copying macros from one project to another. These libraries contain the primitives and macros that you use to build your design.

The Foundation design entry tools contain two types of libraries: system libraries and user libraries.

- System libraries, which are supplied with the Foundation design entry tools, contain sets of components for each device family as well as for simulation. System library contents cannot be modified. The Foundation system libraries include: simprims, xabelsim, xc4000e, xc4000x, xc9500, spartan, spartanx, and virtex.

- User libraries contain user-defined components. Each project has

at least one user library known as the project working library. The

project working library is named the same as the project and is

located in the LIB subdirectory of the project directory. The

Library Manager automatically places any user-created macro in

the current project's working library.

You can access the Library Manager from the Project Manager by selecting Tools  $\rightarrow$  Utilities  $\rightarrow$  Schematic Symbol Library Manager. Refer to the online help accessed from the Library

Manager window for details on how to use the Library Manager. Or, select  $\texttt{Help} \to \texttt{Foundation}$  Help Contents $\to \texttt{Advanced}$   $\texttt{Tools} \to \texttt{Symbol}$  Library Manager.

## **Command History**

Command History (Tools  $\rightarrow$  Utilities  $\rightarrow$  Command History) sequentially lists the processes that have been performed for the selected revision. You can select from two different modes: 1) Process, which displays the name of the process only, and 2) Command Line, which displays the full command line of each process. An option to display the date and time for each command is also available.

#### **Project Notes**

Project Notes (Tools  $\rightarrow$  Utilities  $\rightarrow$  Project Notes) opens a standard text editor of your choice in which you can make notes for the current project. Specify the text editor in the Configuration dialog (File  $\rightarrow$  Preferences  $\rightarrow$  Configuration).

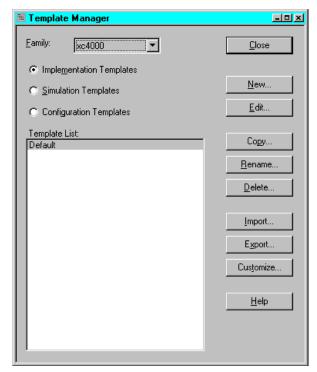

## **Implementation Template Manager**

The Implementation Template Manager can create or modify three types of templates for a selected device: implementation, simulation, and configuration. Implementation templates control how an FPGA design is mapped, optimized, placed, and routed and how a CPLD design is fitted. Simulation templates control the creation of netlists for front- and back-end simulation. Configuration templates control the configuration startup, readback, and parameters for the device.

#### ABEL to VHDL/Verilog Converter

The ABEL2HDL utility accessed from **Tools** → **Utilities** → **ABEL2HL** in the Project Manager allows you to select an ABEL (.abl) file and have it converted to a VHDL (.vhd) or Verilog (.v) file.

## Altera HDL to VHDL/Verilog Converter

The AHDL2HDL utility accessed from Tools  $\rightarrow$  Utilities  $\rightarrow$  AHDL2HDL in the Project Manager allows you to select an Altera HDL (.tdf) file and have it converted to a VHDL (.vhd) or Verilog (.v) file.

# **Design Methodologies - Schematic Flow**

This chapter describes various design methodologies supported in the Schematic Flow project subtype.

This chapter contains the following sections.

- "Schematic Flow Processing Overview"

- "Top-Level Designs"

- "All-Schematic Designs"

- "Schematic Designs with Instantiated HDL-Based Macros"

- "Schematic Designs With Instantiated LogiBLOX Modules"

- "Schematic Designs With Instantiated CORE Generator Cores"

- "Schematic Designs With Finite State Machine (FSM) Macros"

- "Finite State Machine (FSM) Designs"

# **Schematic Flow Processing Overview**

Refer to the "Project Toolset" chapter for information on how to create a Schematic Flow project and for an overview of the tools available for such projects.

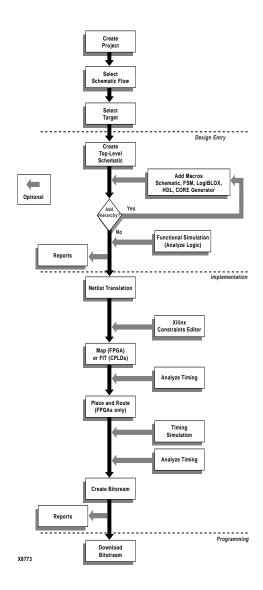

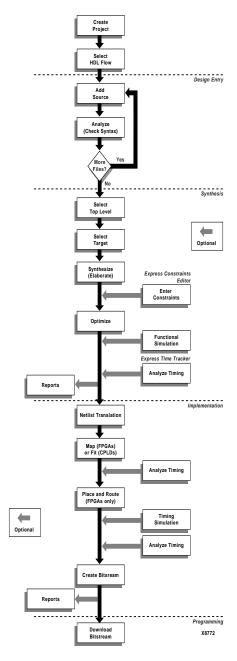

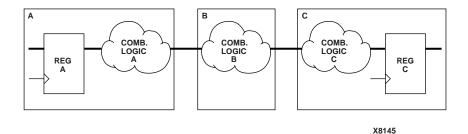

The following figure illustrates the processing performed at the various stages of a Schematic Flow project.

Figure 3-1 Schematic Flow Project Processing

# **Top-Level Designs**

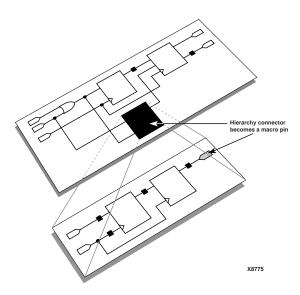

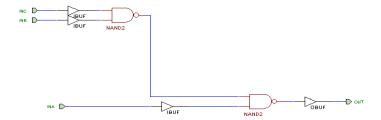

Schematic Flow projects can have top-level schematic or Finite State Machine (ABEL) designs. A top-level design can have any number of underlying schematic, HDL, LogiBLOX, CORE Generator, ABEL, or Finite State Machine (FSM) macros. Although individual modules may require some form of synthesis, the entire project is not synthesized and the netlist that is exported for implementation is not optimized across module boundaries as in an HDL Flow project.

# **All-Schematic Designs**

The following procedure describes how to create a top-level schematic design that contains schematics only, that is, there are no instantiated HDL or State Machine macros.

## **Creating the Schematic and Generating a Netlist**

This section lists the basic steps for creating a schematic and generating a netlist from it.

1. Open the Schematic Editor by selecting the Schematic Editor icon from the Design Entry box on the Project Manager's Flow tab.

- 2. Select Mode → Symbols to add components to your new schematic. Select specific components from the SC Symbols window.

- 3. Complete your schematic by placing additional components from the Symbol toolbox including I/O ports, nets, buses, labels, and attributes.

- 4. Save your schematic by selecting File  $\rightarrow$  Save.

For more information about schematic designs, see the "Schematic Design Entry" chapter or in the Schematic Editor window, select  $\mathtt{Help} \to \mathtt{Schematic}$  Editor  $\mathtt{Help}$  Contents.

## **Performing Functional Simulation**

1. Open the Logic Simulator by clicking the Functional Simulation icon in the Simulation box on the Project Manager's Flow tab.

The design is automatically loaded into the simulator. The Waveform Viewer window displays on top of the Logic Simulator window.

- 2. Add signals by selecting Signal  $\rightarrow$  Add Signals.

- From the Signals Selection portion of the Components Selection for Waveform Viewer window, select the signals that you want to see in the simulator.

- Use CTRL-click to select multiple signals. Make sure you add output signals as well as input signals.

- 5. Click Add and then Close. The signals are added to the Waveform Viewer in the Logic Simulator screen.

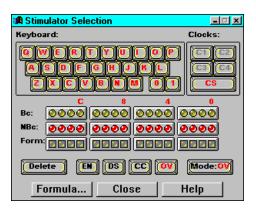

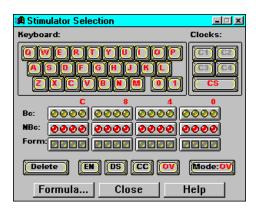

- 6. Select  $signal \rightarrow Add$  Stimulators from the Logic Simulator menu. The Stimulator Selection window displays.

- 7. In the Stimulator Selection window, create the waveform stimulus by attaching stimulus to the inputs. For more details on how to use the Stimulus Selection window, click the Help button.

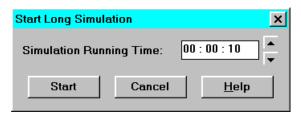

- 8. After the stimulus has been applied to all inputs, click the Simulation Step icon on the Logic Simulator toolbar to perform a simulation step. The length of the step can be changed in the Simulation Step Value pulldown menu to the right of the Simulation Step box. (If the Simulator window is not open, select View → Main Toolbar

- 9. Verify that the output waveform is correct. Click the Step button repeatedly to continue simulating.

- 10. To save the stimulus for future viewing or reuse, select File → Save Waveform. Enter a file name with a .tve extension in the File name box of the Save Waveform window. Click OK.

For more information about saving and loading test vectors, from the Logic Simulator window, select  $\mathtt{Help} \to \mathtt{Logic}$  Simulator  $\mathtt{Help}$  Contents. Then select Simulator Reference  $\to \mathtt{Working}$  WithWaveforms  $\to \mathtt{Saving}$  and Loading Waveforms.

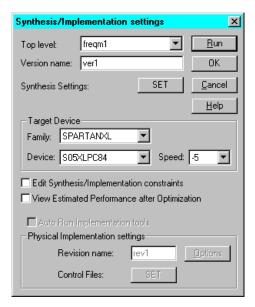

## Implementing the Design

Click the Implementation icon in the Implementation box on the Project Manager's Flow tab.

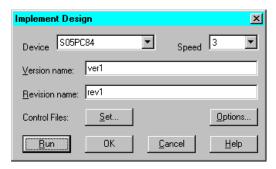

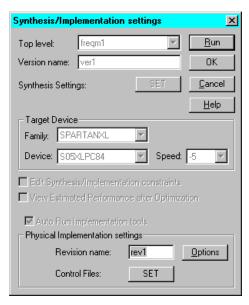

2. The Implement Design dialog box appears.

By default, the Implementation targets the device that was previously selected when you created the project. If you want to

retarget the design to a different device, use the Implement Design dialog box. If you want to retarget to a new device family, you must first do so in the Foundation Project Manager by selecting  $\mathtt{File} \rightarrow \mathtt{Project}$  Type.

The first time you implement the design, a new version of the design is created and given the default version and revision name shown in the Implement Design dialog box. You can modify the version and revision names as desired.

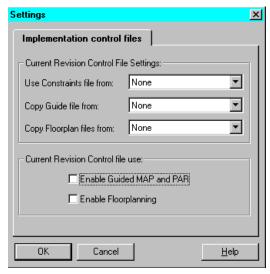

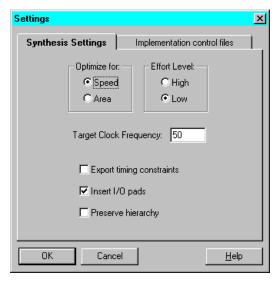

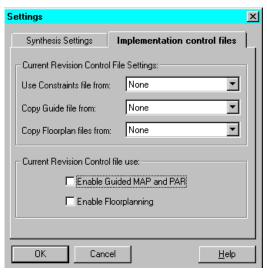

3. In the Implement Designs dialog box, select *Set*. The Settings dialog box appears.

- 4. Specify control files if desired. Click **OK** to return to the Implement Design dialog box.

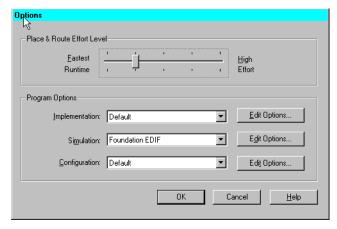

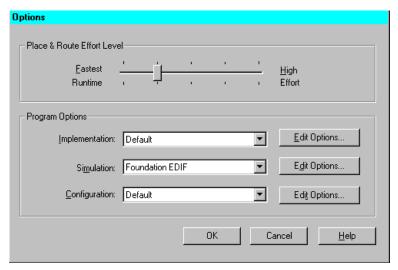

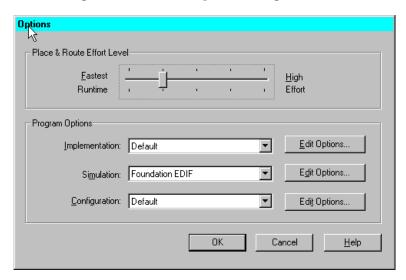

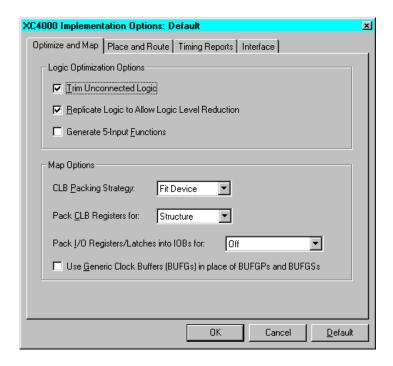

- 5. In the Implement Design dialog box, select Options. The Options dialog box displays.

- 6. Choose any desired implementation options.

- 7. Click **ok** to return to the Implement Design dialog box.

- 8. Click **Run** to implement your design. The Flow Engine displays the progress of the implementation.

When Implementation is complete, a dialog box appears indicating whether implementation was successful or not.

For more information on the Flow Engine, refer to the "Design Implementation" chapter or select  $\mathtt{Help} \to \mathtt{Foundation}$  Help Contents  $\to \mathtt{Flow}$  Engine.

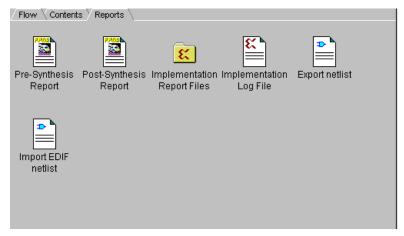

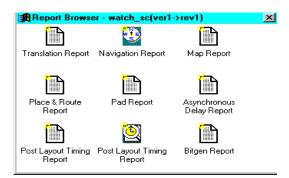

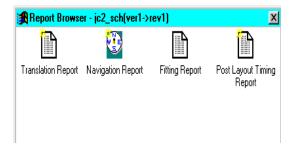

9. Select the Reports tab on the Project Manager window and then double click the Implementation Report Files folder. Double click a report icon to review your design reports.

#### **Creating a New Revision**

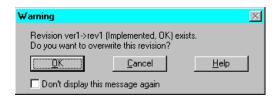

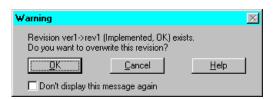

If you modify the design, then click the Implementation button to reimplement the design after the first revision of a design version has been implemented, the existing revision is overwritten. A warning box appears to allow you to verify the overwrite operation.

You do not access the Implement Design dialog box for subsequent versions/revisions.

If you want to implement a new revision of the design (for any version), you must first create the new revision by selecting Project  $\rightarrow$  Create Revision. This accesses the Create Revision dialog box that has the same fields as the Implement Design dialog box. The revision name is automatically entered. Modify the names, control files, and/or options and run the Flow Engine as described previously for the first version/revision.

#### **Creating a New Version**

## **Editing Implementation Constraints**

Constraints are instructions placed on symbols or nets in a schematic (or textual entry file such as VHDL or Verilog). They affect how the logical design is implemented in the target device. Applying constraints helps you to adapt your design's performance to expected worst-case conditions. The user constraint file (.ucf) is an ASCII file that holds timing and location constraints. It is read (by NGDBuild) during the translate process in the Flow Engine and is combined with an EDIF or XNF netlist into an NGD file.

In Foundation, a UCF file is automatically associated with a Revision. This UCF file is copied and used as your UCF file within a new revision. You can directly enter constraints in the UCF file or you can use the Xilinx Constraints Editor.

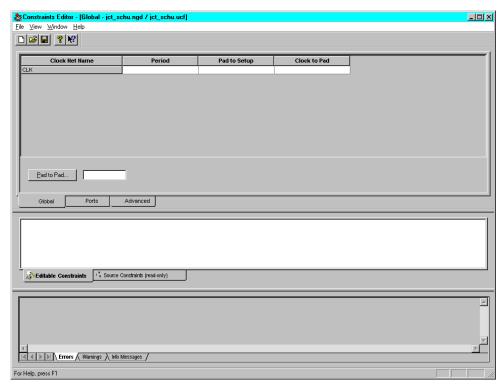

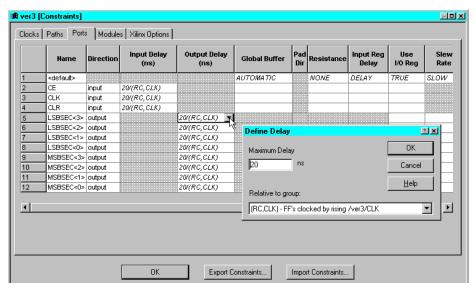

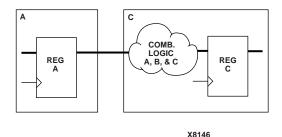

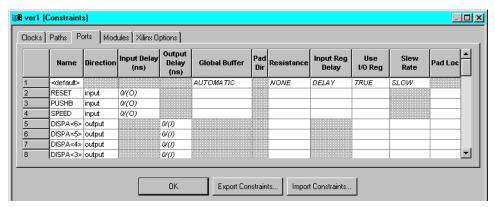

The Constraints Editor is a Graphical User Interface (GUI) that you can run after the Translate program to create new constraints in a UCF file. To access the Constraints Editor, select Tools → Implementation → Constraints Editor from the Project Manager.

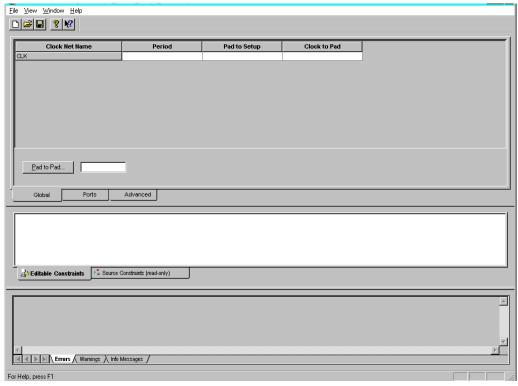

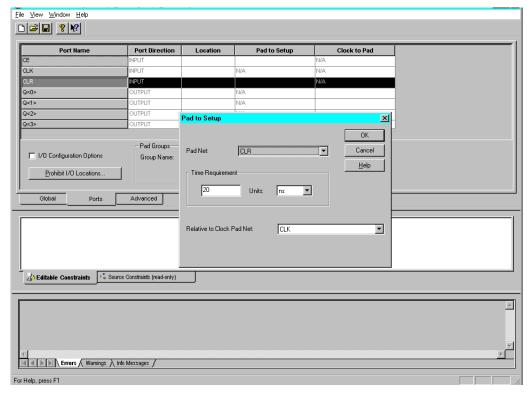

The following figure shows an example of the Global tab of the Implementation Constraints Editor.

- Design-specific information is extracted from the design and displayed in device-specific spreadsheets. Click the tabs to access the various spreadsheets.

- 3. Right-click on an item in any of the spreadsheets to access a dialog box to edit the value. Use the online help in the dialog boxes to understand and enter specific constraints and options. Or, refer to the online software document, *Constraints Editor Guide* for detailed information.

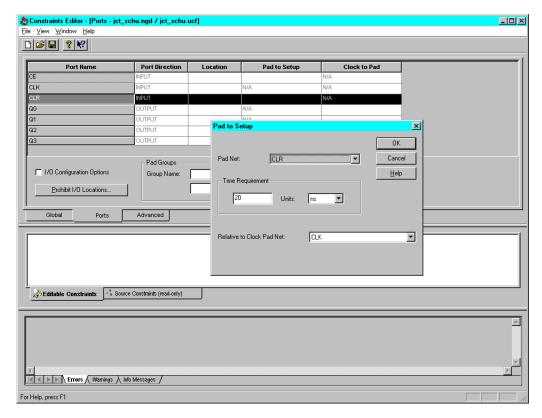

The following figure shows an example of the Pad to Setup dialog box accessed when you right click anywhere on the CLR Port row on the Ports tab of the Implementation Constraints Editor and then select Pad to Setup.

Figure 3-2 Implementation Constraints Editor - Ports Tab

- 4. After you finish editing the constraints, click **Save** to close the Constraints Editor window

- 5. You must rerun the Translate step in the Flow Engine to have your new constraints applied to the design.

- 6. Click the Implementation icon on the Project Manager's Flow tab to rerun Translate (and the other phases).

Or, to just rerun the Translate phase, select Tools  $\rightarrow$  Implementation  $\rightarrow$  Flow Engine. Click Yes to start at the Translate phase when prompted. Then click the Step button at the bottom of the Flow Engine Window window. Exit the Flow Engine when the Translate phase is Completed.

## Verifying the Design

#### **Performing a Static Timing Analysis (Optional)**

1. Click the Timing Analyzer icon in the Verification box on the Project Manager's Flow tab.

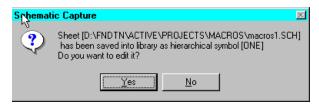

2. Perform a static timing analysis on mapped or placed and routed designs for FPGAs.